Page 27 -

P. 27

CH-CPLD 補充教材

四、功能模擬

當完成專案電路編譯後,便可執行邏輯功能模擬,以驗證專案之邏輯功能,

是否符合實際設計之要求。執行功能模擬,必須先開啟模擬所需波形編輯器

(*.vwf) 視窗,並於波形編輯器設定輸入端的邏輯準位或時序,在下達邏輯功能

模擬指令後,即可得到欲觀察之輸出端與內部節點之邏輯準位。

執行邏輯功能模擬,必須經過下列幾個流程:

z 開啟波形編輯器

z 儲存波形編輯視窗

z 選取欲進行波形分析之輸入端、輸出端或節點

z 編輯各個輸入節點的邏輯準位

z 執行功能模擬

1.開啟波形編輯器

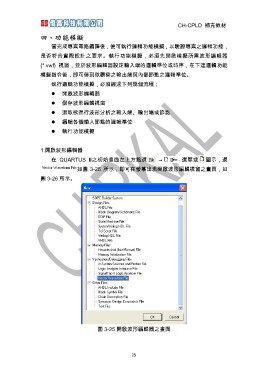

在 QUARTUS Ⅱ之初始畫面左上方點選 → 選單或 圖示,選

如圖 3-25 所示,即可在螢幕出現開啟波形編輯視窗之畫面,如

圖 3-26 所示。

圖 3-25 開啟波形編輯器之畫面

25