Page 85 -

P. 85

CH-CPLD 補充教材

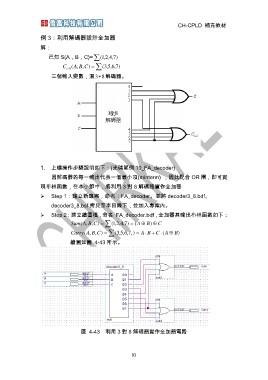

例 3:利用解碼器設計全加器

解:

已知 S(A,B,C)= ∑(1,2,4,7)

∑Ci−1( A, B,C) = (3,5,6,7)

三個輸入變數,選 3∗8 解碼器。

1. 上機操作步驟說明如下:(光碟範例 10_FA_decoder)

因解碼器的每一輸出代表一個最小項(minterm) ,因此配合 OR 閘,即可實

現布林函數,在本小節中,將利用 3 對 8 解碼器實作全加器

¾ Step 1:建立新專案,命名:FA_decoder。並將 decoder3_8.bdf、

decoder3_8.bsf 拷貝至本目錄下,並加入專案內。

¾ Step 2:建立繪圖檔,命名 FA_decoder.bdf,全加器其輸出布林函數如下:

Sum( A, B,C) = ∑ (1,2,4,7) = ( A ⊕ B) ⊕ C

Carry( A, B,C) = ∑ (3,5,6,7, ) = A ⋅ B + C ⋅ ( A ⊕ B)

繪圖如圖 4-43 所示。

圖 4-43 利用 3 對 8 解碼器實作全加器電路

83