Page 47 -

P. 47

CH-CPLD 補充教材

第伍章 CPLD 範例程式(組合邏輯電路)

本章重點:

1.加法器設計。2.BCD 加法器設計。3.解碼器設計與應用。

4.多工器設計與應用。5.數碼轉換器設計

一、實驗項目:組合邏輯設計步驟

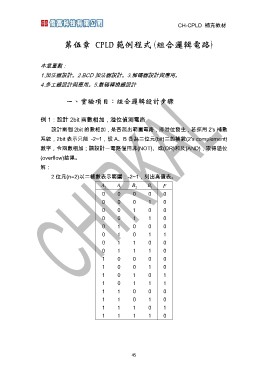

例 1:設計 2bit 兩數相加,溢位偵測電路

設計兩個 2bit 的數相加,是否超出範圍電路,即溢位發生,若採用 2's 補數

系統,2bit 表示只能 -2~1,設 A、B 各為二位元(bit)二的補數(2's complement)

數字,令兩數相加;請設計一電路僅用非(NOT)、或(OR)和及(AND),取得溢位

(overflow)結果。

解:

2 位元(n=2)以二補數表示範圍:-2~1,列出真值表。

A2 A1 B2 B1 F

0 0 0 00

0 0 0 10

0 0 1 00

0 0 1 10

0 1 0 00

0 1 0 11

0 1 1 00

0 1 1 10

1 0 0 00

1 0 0 10

1 0 1 01

1 0 1 11

1 1 0 00

1 1 0 10

1 1 1 01

1 1 1 10

45