Page 41 -

P. 41

CH-CPLD 補充教材

五、接腳指定

在完成專案設計之邏輯功能模擬,並驗證輸入與輸出節點之邏輯準位,皆符

合原始電路設計之要求後,接著進行晶片腳位設定,即輸入與輸出節點對應至選

用 FPGA/CPLD 晶片腳位。回註腳位設定 (Back-Annotate Assignments) 為

QUARTUS Ⅱ較常用來實現 CPLD 晶片腳位設定之方法,而使用回註腳位設定

來完成晶片腳位設定之流程如下:

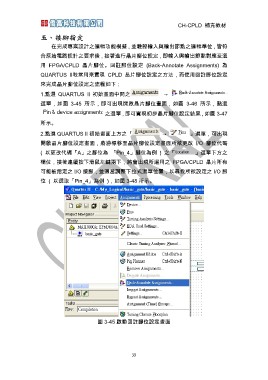

1.點選 QUARTUS II 初始畫面中間之 →

選單,如圖 3-45 所示,即可出現開啟晶片腳位畫面,如圖 3-46 所示,點選

之選單,即可實現初步晶片腳位設定結果,如圖 3-47

所示。

2.點選 QUARTUS II 初始畫面上方之「 → 」選單,可出現

開啟晶片腳位設定畫面,將游標移至晶片腳位設定畫面所欲更改 I/O 腳位代碼

( 以更改代碼「A」之腳位為 「Pin_4」腳位為例 ) 之「 」選單下方之

欄位,接著連續按下滑鼠左鍵兩下,將會出現所選用之 FPGA/CPLD 晶片所有

可能被指定之 I/O 接腳,並適當調整下拉式選單位置,以尋找所欲設定之 I/O 腳

位 ( 以選取「Pin_4」為例 ),如圖 3-48 所示。

圖 3-45 啟動回註腳位設定畫面

39