Page 82 -

P. 82

依 INT0、Timer0、INT1、Timer1、UART 之順序先後執行。

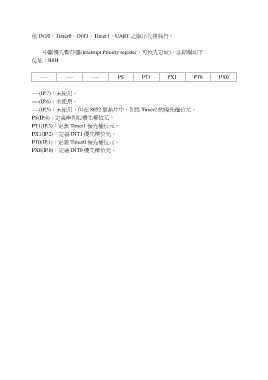

中斷優先暫存器(Interrupt Priority register,可位先定址),其結構如下:

位址:B8H

---- ---- ---- PS PT1 PX1 PT0 PX0

----(IP.7):未使用。

----(IP.6):未使用。

----(IP.5):未使用,但在 8052 單晶片中,則為 Timer2 的優先權位元。

PS(IP.4):定義串列埠優先權位元。

PT1(IP.3):定義 Timer1 優先權位元。

PX1(IP.2):定義 INT1 優先權位元。

PT0(IP.1):定義 Timer0 優先權位元。

PX0(IP.0):定義 INT0 優先權位元。