Page 81 -

P. 81

中斷源 INT0 與 INT1 分別位於 8051 單晶片接腳第 12 與 13 支,當此二接腳為低電

位(或〝0〞)時,則 IE0 與 IE1 會設定為〝1〞;而當對應之中斷服務副程式執行完畢後,

則 8051 會自動清除 IE0 與 IE1 旗標。Timer0 與 Timer1 的中斷產生則如第六章所介紹,

當計時/計數值產生溢位時,則對應之旗標 TF0 與 TF1 設定為〝1〞;而當對應之中斷服

務副程式執行完畢後,則 8051 會自動清除 TF0 與 TF1 旗標。UART 為串列埠中斷源,

當串列埠做為傳送或接收時其對應不同的旗標 TI 與 RI,其使用方式將在下一章介紹,

當其對應旗標設定為〝1〞後,且中斷致能,則中斷服務副程式將會執行。當對應之中

斷服務副程式執行完畢後,則 8051 會自動清除 TI 與 RI 旗標。

中斷致能暫存器(Interrupter Enable register,簡稱 IE,可位元定址)用於致能中斷的

發生,若被致能,則中斷發生後將執行中斷服務副程式,否則即使中斷發生亦不會執行

中斷服務副程式。

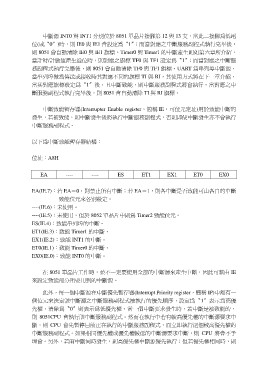

以下為中斷致能暫存器結構:

位址:A8H

EA ---- ---- ES ET1 EX1 ET0 EX0

EA(IE.7):若 EA=0,則禁止所有中斷;若 EA=1,則各中斷是否致能可由各自的中斷

致能位元來各別設定。

----(IE.6):未使用。

----(IE.5):未使用,但於 8052 單晶片中則為 Timer2 致能位元。

ES(IE.4):致能串列埠的中斷。

ET1(IE.3):致能 Timer1 的中斷。

EX1(IE.2):致能 INT1 的中斷。

ET0(IE.1):致能 Timer0 的中斷。

EX0(IE.0):致能 INT0 的中斷。

在 8051 單晶片工作時,並不一定要使用全部的中斷源來產生中斷,因此可藉由 IE

來設定致能部分所要用到的中斷源。

此外,每一個中斷源在中斷優先暫存器(Interrupt Priority register,簡稱 IP)中都有一

個位元來決定該中斷源之中斷服務副程式被執行的優先順序,設定為〝1〞表示為高優

先權,清除為〝0〞則表示為低優先權。當一個中斷要求發生時,若中斷是被致能的,

則 8051CPU 會執行該中斷服務副程式。然而在執行中若有較高優先權的中斷源要求中

斷,則 CPU 會先暫停目前正在執行的中斷服務副程式,而立即執行這個較高優先權的

中斷服務副程式。如果相同優先權或優先權較低的中斷源要求中斷,則 CPU 將會不予

理會。另外,若兩中斷同時發生,則高優先權中斷源優先執行;但若優先權相同時,則