Page 162 -

P. 162

CH-CPLD 補充教材

五、序向邏輯電路設計

¾ 序向電路設計步驟

1. 文字描述(題意),轉換成狀態圖(state diagram)。

2. 將狀態圖轉換成狀態表(state table)。

3. 狀態化簡(state reduced)。

4. 決定正反器個數(若 m 個狀態,需 n 個正反器,使得 m ≤ 2n ),及命名。

5. 狀態指定(state assignment)。

6. 決定正反器型別。

7. 由狀態表倒出激勵表與輸出表。

8. 化簡寫出正反器輸入函數與輸出函數。

9. 繪邏輯圖。

¾ 序向電路設計重點求出正反器的輸入函數與整個電路的輸出函數。

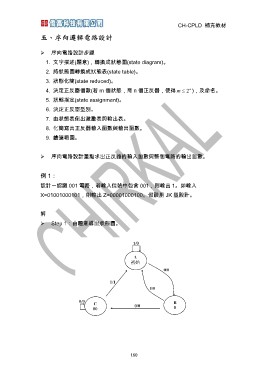

例 1:

設計一認識 001 電路,若輸入信號中包含 001,則輸出 1。如輸入

X=01001000101,則輸出 Z=00001000100。假設用 JK 型設計。

解

¾ Step 1:由題意導出狀態圖。

160