Page 128 -

P. 128

CH-CPLD 補充教材

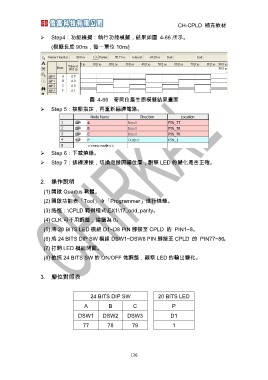

¾ Step4:功能模擬:執行功能模擬,結果如圖 4-66 所示。

(模擬長度 90ns,每一單位 10ns)

圖 4-66 奇同位產生器模擬結果畫面

¾ Step 5:接腳指定,再重新編譯電路。

¾ Step 6:下載燒錄。

¾ Step 7:排線連接,切換指撥開關位置,觀察 LED 的變化是否正確。

2. 操作說明

(1) 開啟 Quartus 軟體。

(2) 開啟功能表「Tool」Æ「Programmer」進行燒錄。

(3) 路徑:\CPLD 範例程式\EX1\17_odd_parity。

(4) CLK 可不用調整,建議為 0。

(5) 將 20 BITS LED 模組 D1~D8 PIN 腳接至 CPLD 的 PIN1~8。

(6) 將 24 BITS DIP SW 模組 DSW1~DSW8 PIN 腳接至 CPLD 的 PIN77~86。

(7) 打開 LED 模組開關。

(8) 依照 24 BITS SW 的 ON/OFF 做調整,觀察 LED 的輸出變化。

3. 腳位對照表

24 BITS DIP SW 20 BITS LED

ABC P

DSW1 DSW2 DSW3 D1

77 78 79 1

126